# Status on ETM

SungHyun Kim

Hanyang University

TRG DAQ Workshop

Aug. 2017

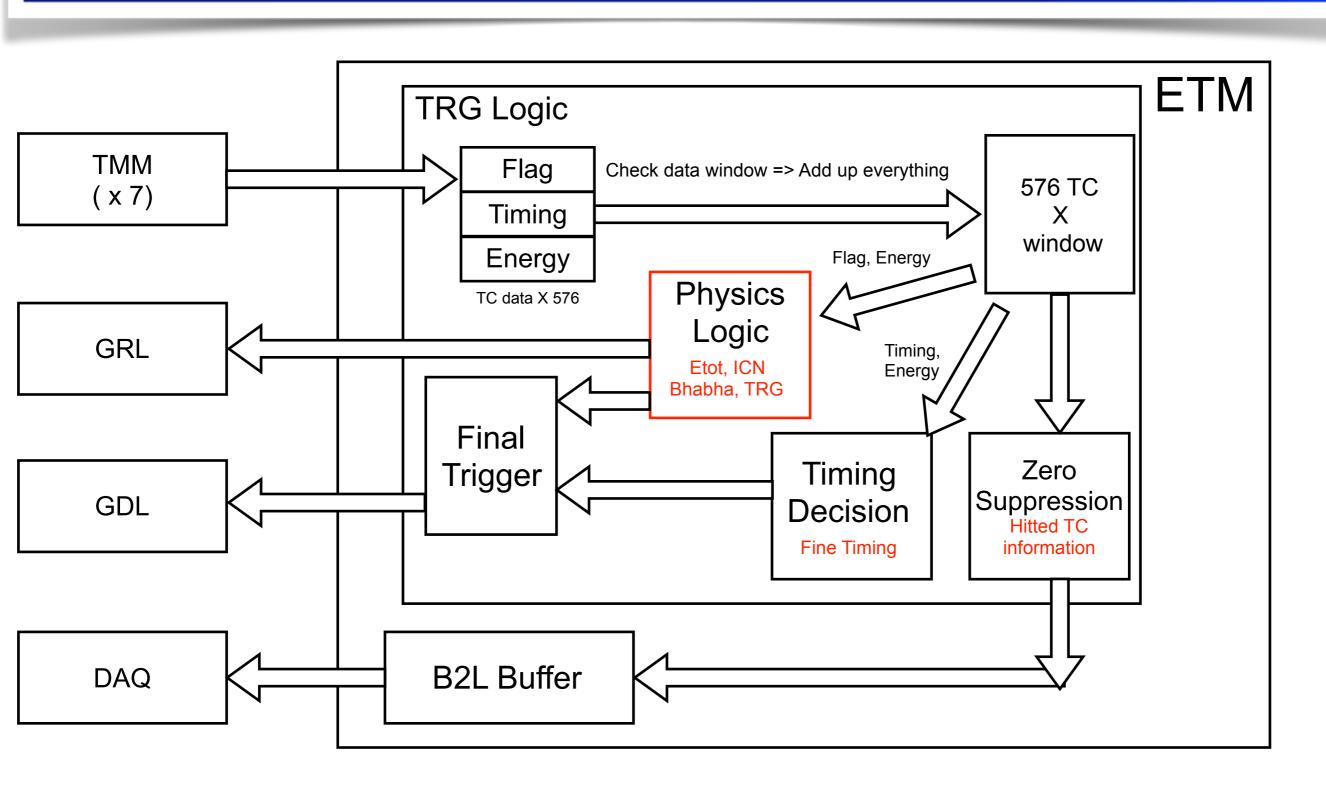

#### Contents

- Latency Measurement

- ECL-TRG Timing Decision Logic Update

- Other Logic Update

- Zero Suppression

- To-Do List

## Latency Check

Measure latency from Scintillator to GDL @ Detector by Nakazawa-san.

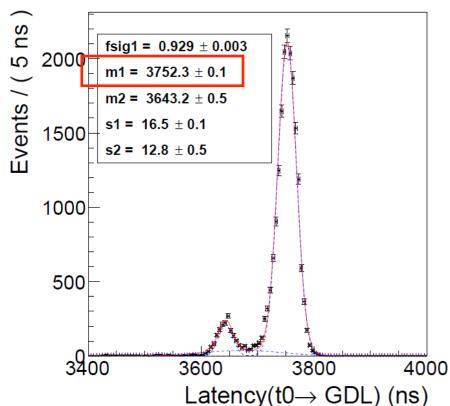

#### Double peak ecltrg trigger timing

- Double peak trigger timing was found by GDL and reported by Nakazawa-san.

- ~125ns timing difference.

- Alex also reported ~100ns trigger timing in ECL data taken based on a trigger by only ECL trigger.

- Confirmed double peak trigger timing at B2 setup.

- •Found in CDC data by Taniguchi-san too.

- But actually triple peak in CDC data…

ECL-Meeting: 12th May, 2017

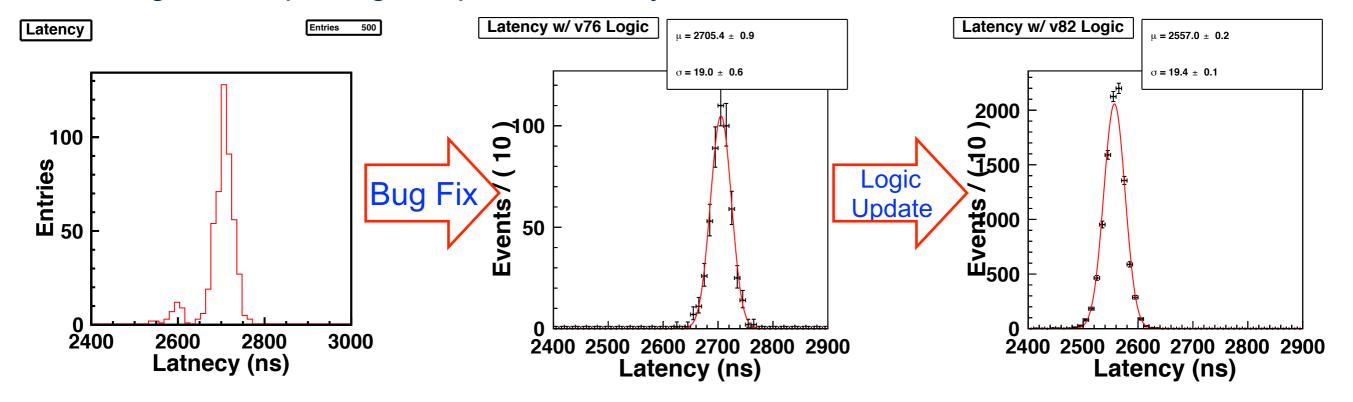

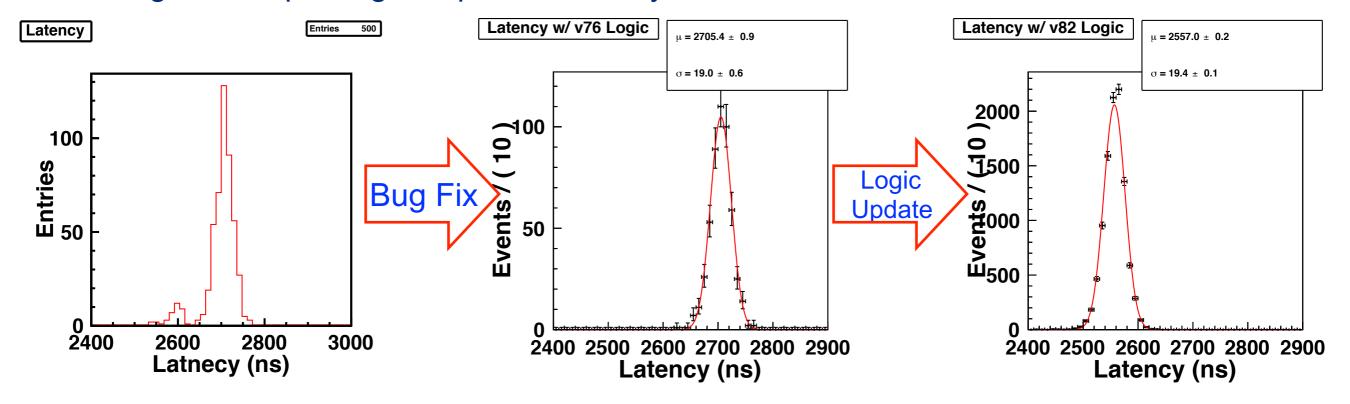

#### Update Logic and Measure Latency

- 1. Fix the double peak problem

- 2. Update TRG Logic

- Using B2 setup, we got improved latency.

| Latency (ns) | EH     | B2     |           |

|--------------|--------|--------|-----------|

| Old          | 3752.3 | 2705.4 | 148.4 ns  |

| New          | ????   | 2557.0 | 140.4 115 |

#### Update Logic and Measure Latency

- 1. Fix the double peak problem

- 2. Update TRG Logic

- Using B2 setup, we got improved latency.

Latency (ns)

EH

B2

Old

3752.3

2705.4

New

(3603.9 (expected))

2557.0

Expected Target Latency :  $3800 \text{ ns} = 3600 + \alpha \text{ (bhabha + physics + etc)}$

148.4 ns

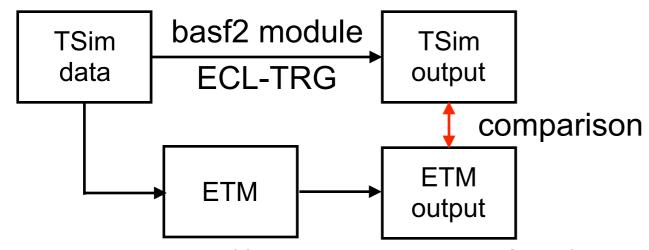

## TSim Study

- In order to check the performance of new ETM logic, we prepare TSim study.

- Add BRAM to ETM firmware for storing TSim data.

- I.S. Lee prepare TSim data

- Condition: 10K Bhabha events, 10K Y(4S) events w/o Beam BG

- Compare the output of ETM firmware and TSim result.

- We have got 99.9% consistency btw TSim & Firmware.

- All inconsistent events occurred because of different data type btw Real(TSim) and Integer(Firmware)

- Integer type TSim or Firmware simulator is needed.

- Here, we compare three items

- Bhabha TRG signal(on/off), ICN, and Total Energy(GeV, second decimal place).

## Belle I type Bhabha Logic

Belle I type Bhabha logic is prepared in ETM firmware.

φ-ring combinations in Belle II enviroment

| C12            | 644         | 646         | -      | -       | ~7    |        |        | C1     | 63       | 63                                      | C4   |

|----------------|-------------|-------------|--------|---------|-------|--------|--------|--------|----------|-----------------------------------------|------|

| C12            | C11         | C10         | C9     | C8      | (/    | 6      | C5     | C4     | C3       | C2                                      | CI   |

| - 170500000 ES | 90000 major | 100-00-0000 | 949030 | 1000000 | 59.39 | 100000 | 550000 | 282 00 | 1.000000 | 100000000000000000000000000000000000000 | 1000 |

B1 B2

Backward

| Combina      | ition (θ id) | Energy cut (F, B : GeV) |     |  |  |  |

|--------------|--------------|-------------------------|-----|--|--|--|

| F1 + F2 + F3 | B1 + B2      | 3.5                     | 1.0 |  |  |  |

| F3           | C12          | 3.0                     | 1.0 |  |  |  |

| F2 + F3      | backward gap | 5.0                     |     |  |  |  |

| C1           | backward gap | 4.0                     | •   |  |  |  |

| C1           | C11 + C12    | 3.5                     | 1.5 |  |  |  |

| C2           | C11 + C12    | 3.5                     | 1.5 |  |  |  |

| C1 + C2      | C11          | 3.5                     | 1.5 |  |  |  |

| C2           | C10 + C11    | 3.5                     | 1.5 |  |  |  |

| C2           | C9 + C10     | 3.5                     | 1.5 |  |  |  |

| C2 + C3      | C10          | 3.5                     | 1.5 |  |  |  |

| C2 + C3      | C9           | 3.5                     | 1.5 |  |  |  |

| C3 + C4      | C9           | 3.5                     | 1.5 |  |  |  |

| C3 + C4      | C8           | 3.5                     | 1.5 |  |  |  |

| C4 + C5      | C8           | 3.5                     | 1.5 |  |  |  |

| C5           | C7 + C8      | 3.5                     | 3.0 |  |  |  |

| C5 + C6      | C6 + C7      | 3.5                     | 3.0 |  |  |  |

| forward gap  | C11 + C12    |                         | 3.0 |  |  |  |

| forward gap  | B1           | 1                       | 3.0 |  |  |  |

- Belle I type Bhabha Logic

- Φ-ring sum with asymmetric energy cut

- + ICN Logic (Belle I)

- Plan

- $\Phi$ -ring sum(2D)  $\Rightarrow$  3D

- ICN ⇒ Cluster

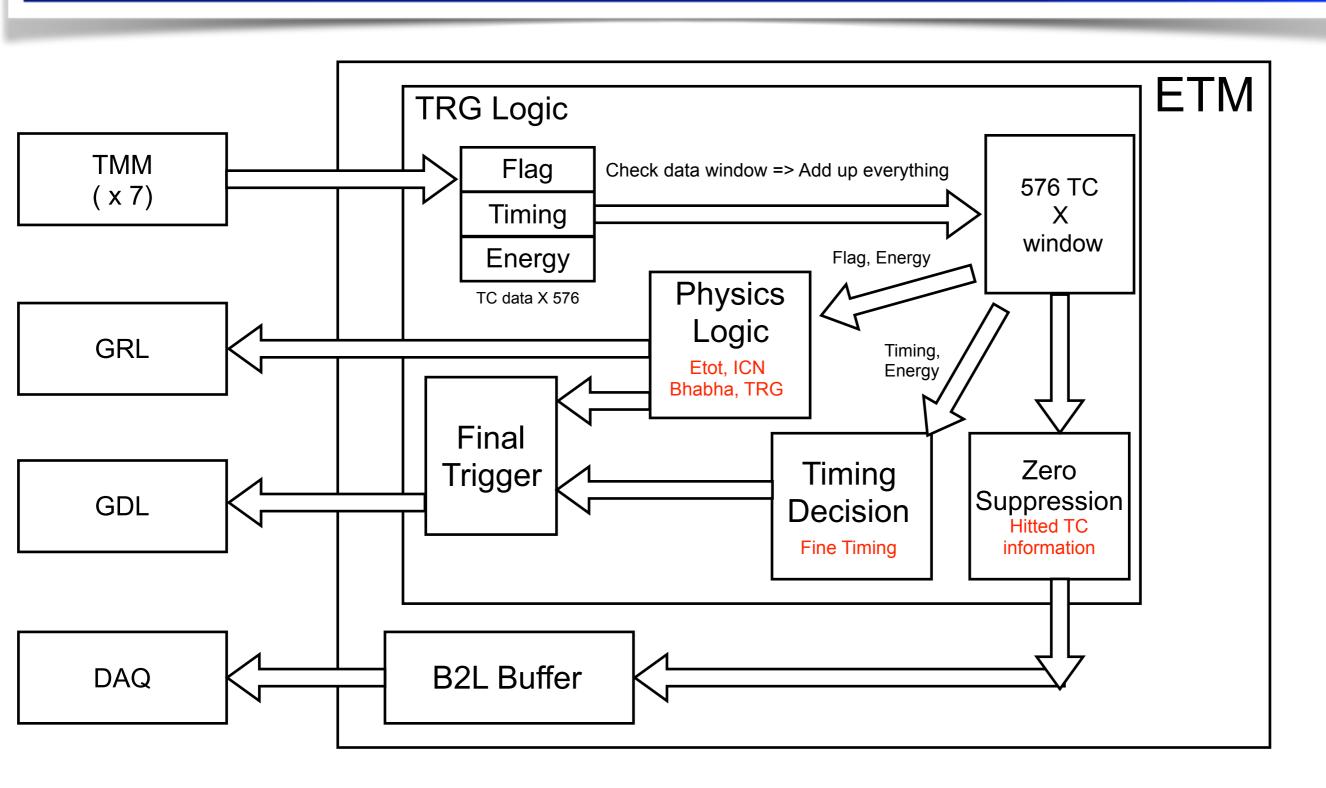

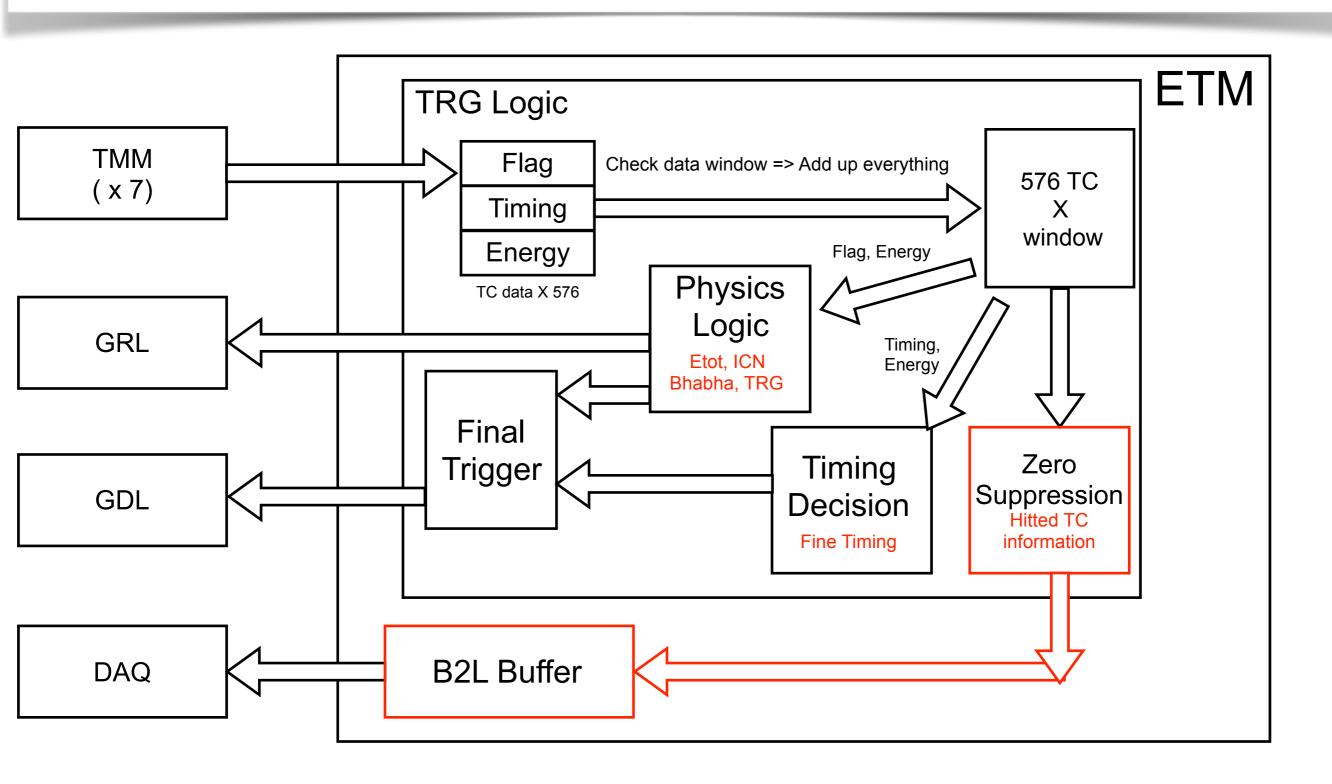

## Zero Suppression

- Current ECL-TRG data size to store dag copper is 12800 bit.

- 576 TC × 22 bit (flag, timing, energy) = 12672 bit +  $\alpha$  (R&D)

- Because of resource limitation in FPGA, ETM can't keep long data in B2L buffer.

- Also timing constraint fit error was happened.

- We decide to reduce data size by suppressing unnecessary TC data.

- Max. # of TC Hit in Total (in firmware): 63 (if needed, can increase)

- TSim: ~30 for Y(4S) w/ BG

- Current Data. : 576 × 22 bit (flag, timing, energy) +  $\alpha \Rightarrow$  12800 bit

- Suppressed Data :

- (Max) 63 × 30 bit +  $\alpha \approx 2000$  bit = (1/6) × current data

- (Bhabha)  $3\sim5 \times 30$  bit +  $\alpha = 100\sim200$  bit

- $(Y(4S)) 10\sim30 \times 30 \text{ bit} + \alpha = 300 \sim 1000 \text{ bit}$

- (30 bit = 10 bit TC ID, 8 bit timing, 12 bit energy)

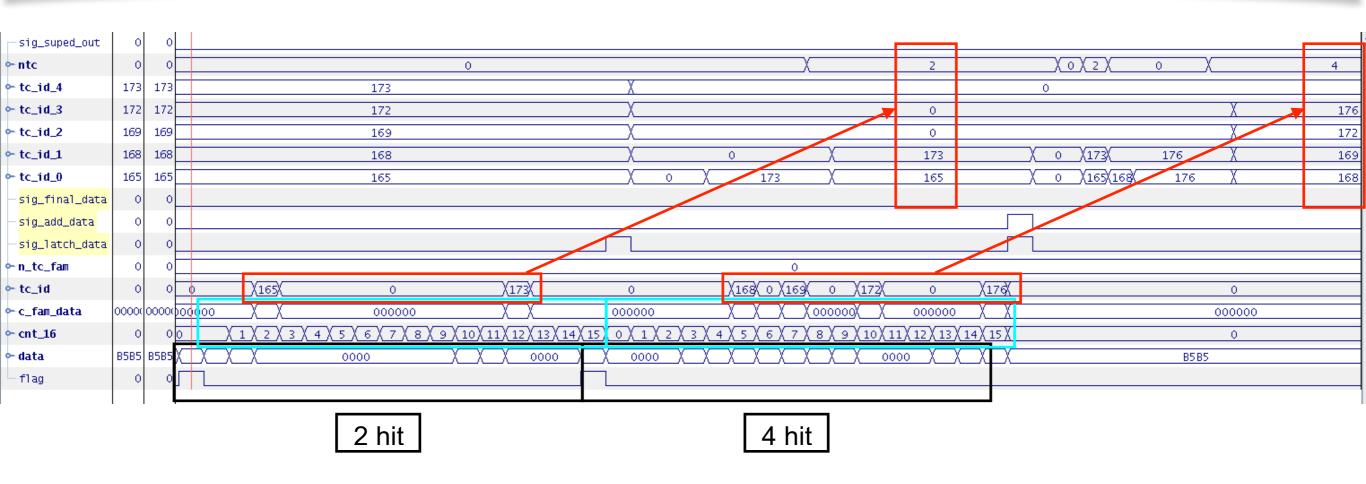

- Using Chipscope, we check our new logic works well.

- B2Link Buffer update is needed.

## Summary / Plan

- ECL-TRG Logic Update

- Double peak problem disappeared.

- Reduce ETM latency.

- Belle I type Bhabha Logic.

- Zero suppression Logic is ready.

- B2Link Buffer modification is needed.

- ETM → GDL: Fine timing (LSF = 1 ns) with ECL-TRG

- ETM → GRL : Dummy Data

- ECL-TRG Logic update

- BG veto logic (~ 1 mon)

- Clustering Logic (~ 1~2 mon)

- 3D Bhabha veto logic (~ 1 mon)

# Backup

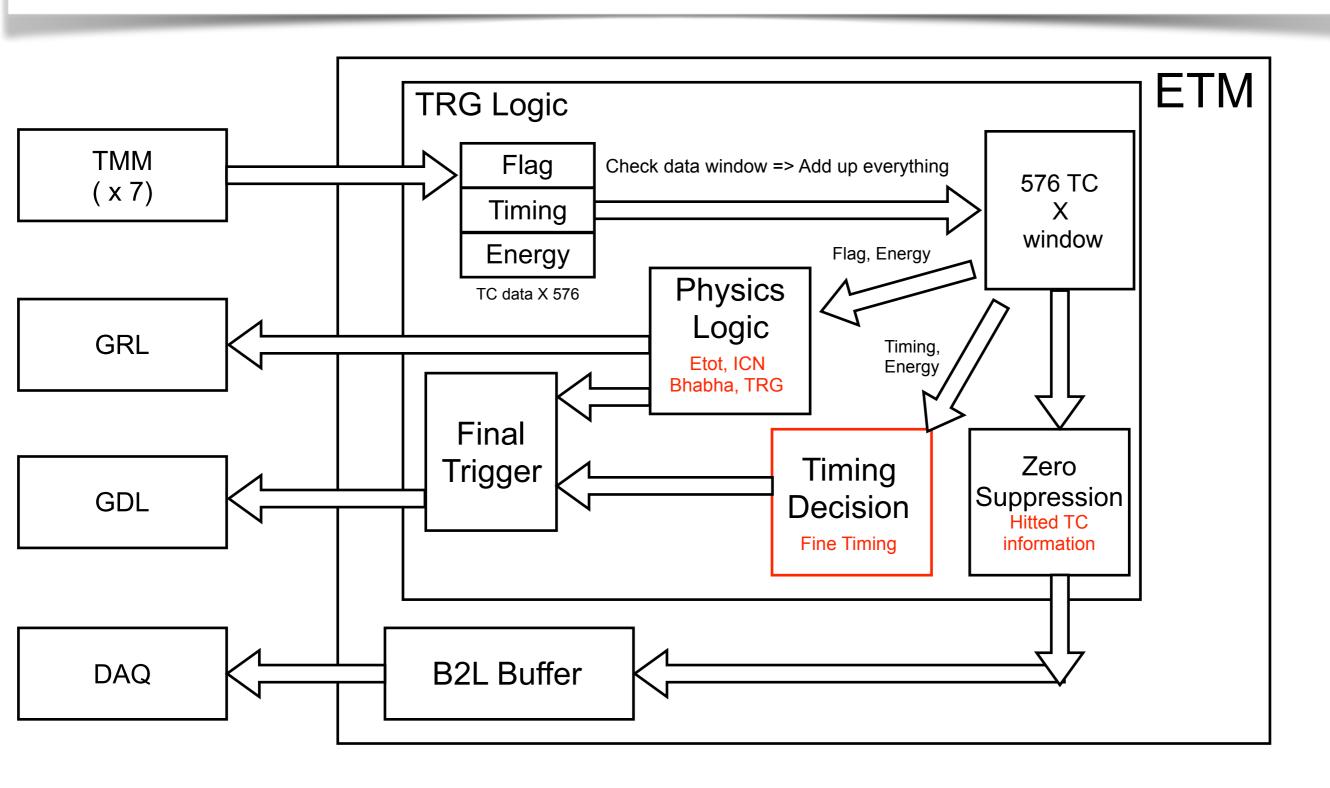

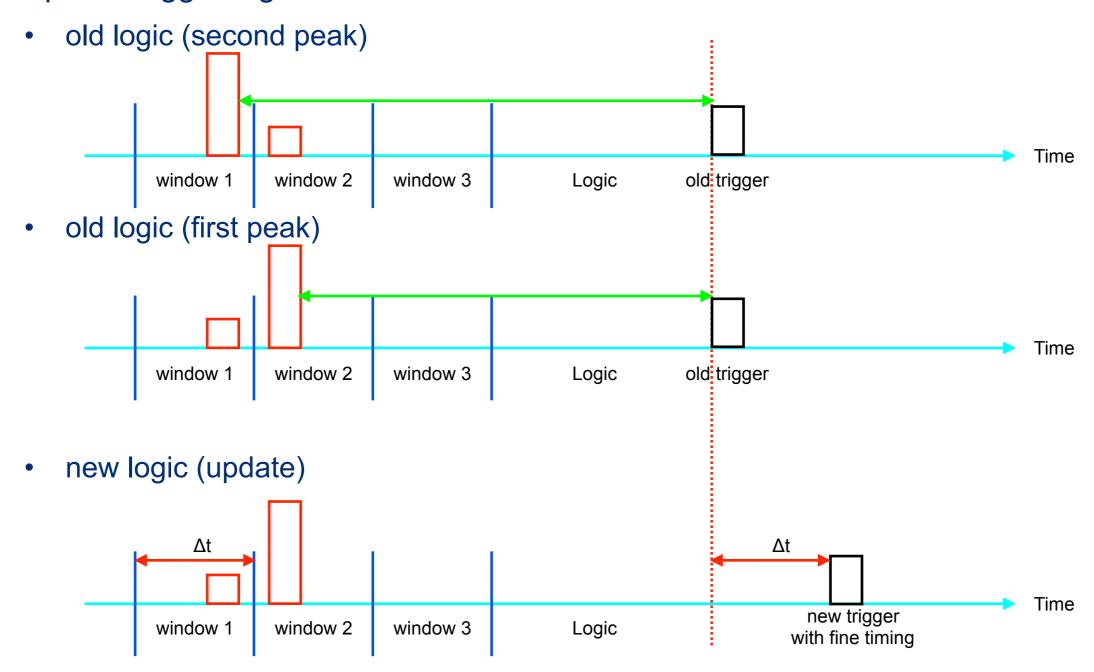

#### ECL-TRG Timing Decision Logic Update (1)

Update trigger logic

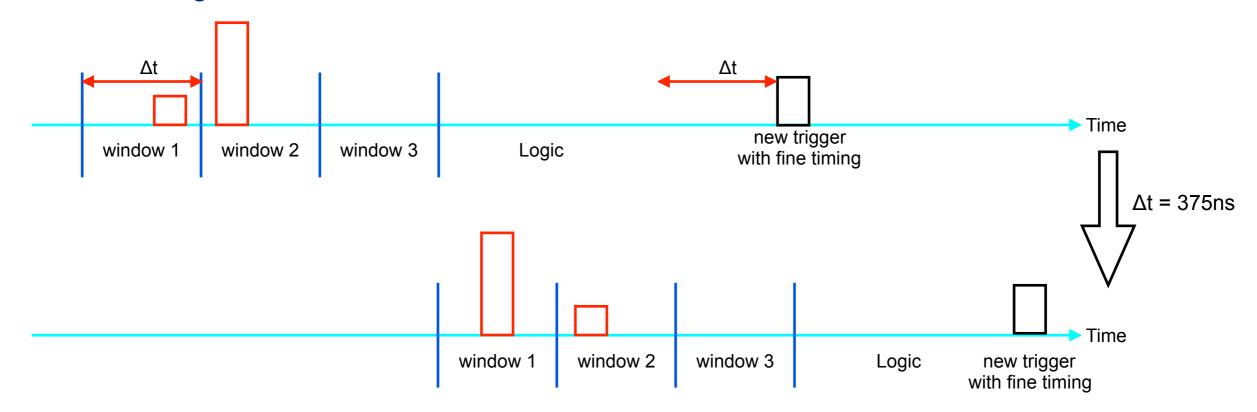

#### ECL-TRG Timing Decision Logic Update (2)

- I realize ETM timing decision logic is different from TSim logic.

- Current Logic

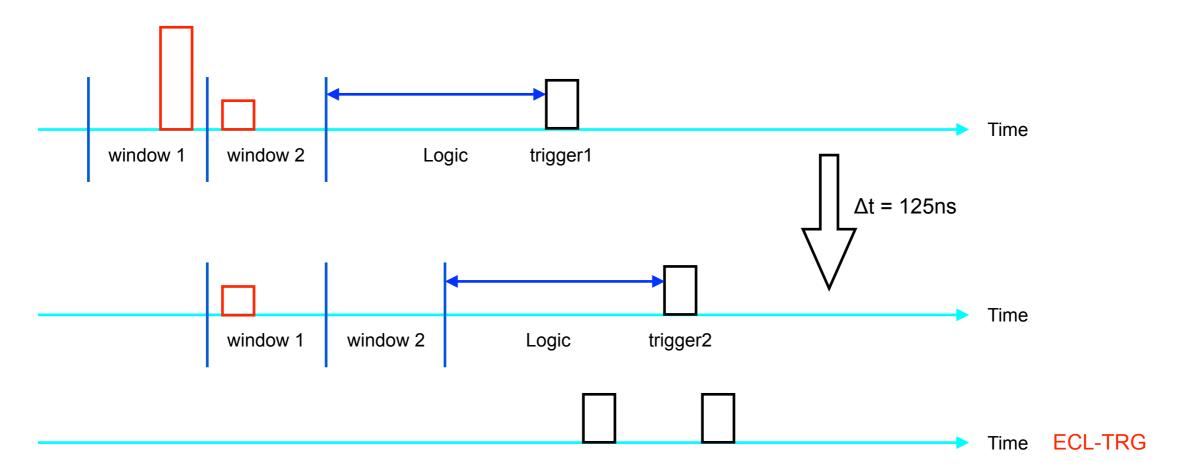

#### ECL-TRG Timing Decision Logic Update (2)

- I realize ETM timing decision logic is different from TSim logic.

- TSim Logic (case 1)

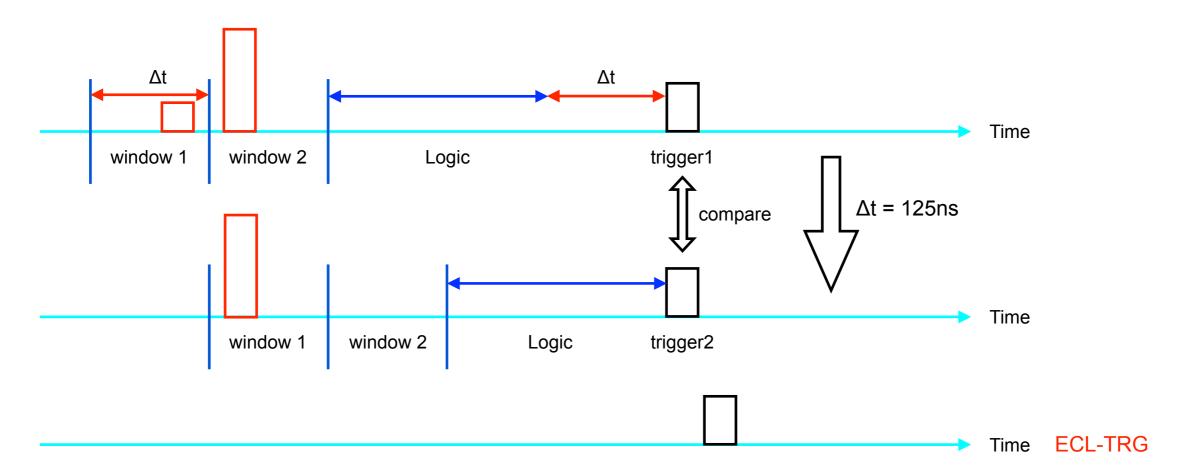

#### ECL-TRG Timing Decision Logic Update (2)

- I realize ETM timing decision logic is different from TSim logic.

- TSim Logic (case 2)

#### Result