## **TOP** Trigger Status

#### Nisar Nellikunnummel Vladimir Savinov

University of Pittsburgh

August 23, 2017

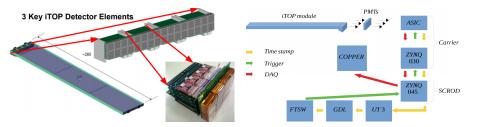

- TOP counter is designed for barrel particle identification

- Its good intrinsic time resolution enables t0 (time of arrival of charged particles on TOP) estimation with ns time resolution

- $\bullet\,$  This t0 helps to reduce data volume of out-of-time hits in SVD

Image: A image: A

#### t0 estimation

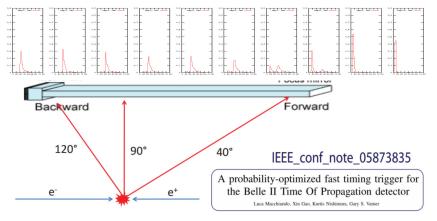

- Timestamps: Time of arrival of photons on PMT

- Photons (timestamps) produced from a charged particle follow some pattern based on the location of hit on the bar

Image: A matrix and a matrix

æ

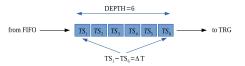

- Timestamps are produced on FEE and send to UT3 using AURORA 8b10b protocol at a line rate 5.08Gbps.

- Timestamping is based on revo9 marker synchronized with the accelerator clock

- revo9 marker is updated every 90us

- Timestamp is represented by the number of clock cycles since most recent revo9 marker

- Clock used for timestamps allows 3ns binning. Therefore 16 bits are sufficient for timestamping (timestamping is done on both edges of axiClk(169 MHz). axiClk= 8 × SSTClk= 8 × FTSWClk/6, FTSWClk = 127 MHz)

- Timestamping at 1ns binning will improve trigger performance

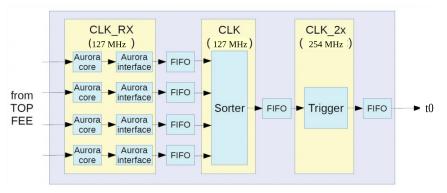

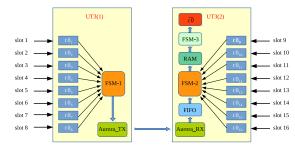

### TOP Trigger Firmware

t0s are estimated separately on each TOP bar and are combined later

- **9** Receive: Timestamps come through 4 channels from FEE

- Sorting: 4 channels are merged and Timestamps are sorted according to time

- O Trigger: t0 is estimated by fitting the Timestamps to PDFs by a Maximum Likelihood Fitting

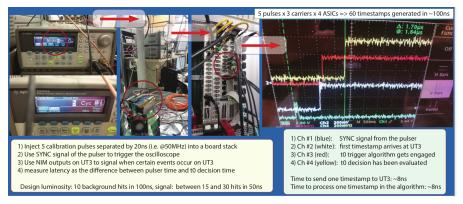

- TOP Trigger FW for single Bar is tested at KEK and estimate trigger rate

- $\bullet\,$  FEE was pulsed with 100 kHz calibration pulses — > we expect t0 decision in every 10 us

- The time interval between adjacent trigger decisions are estimated and they are consistent with the calibration pulses

| 👹 Waveform - DEV  | :0 My | Devic  | ce0 (XC6VHX380T) UNIT:1 MyILA1 (LA)                       | ់ ខា 🗵                                   |

|-------------------|-------|--------|-----------------------------------------------------------|------------------------------------------|

| Bus/Signal        | х     | 0      | 14 -13 -12 -11 -10 -9 -8 -7 -6 -5 -4 -3 -2 -1 0 1 2       | 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 |

| ∾ rx_d<1>         | 7C1C  | 7C1C:  | :<br>                                                     |                                          |

| -valid<1>         | 0     | 0      |                                                           |                                          |

| > rx_d<2>         | 1010  | 1010   |                                                           |                                          |

| -valid<2>         | 0     | 0      |                                                           |                                          |

| ∾ rx_d<3>         | BCBC  | BCBC:  | <u>cicicidý… Xi… Xi… Xi… Xi… Xi… Xi… Xi… Xi… Xi… Xi</u>   | )\$)\$)\$)\$)\$)\$                       |

| -valid<3>         | 0     | 0      |                                                           |                                          |

| <b>∽ rx_d</b> <4> | 1CBC  | 1CBC:  | : <u>)1)6)7)7)1)1)6)6)6</u>                               | )@)@                                     |

| -valid<4>         | 0     | 0      |                                                           |                                          |

| ~ t0              | 1700  | 1700:  | 17001 X                                                   | 20411                                    |

| -trg_fifo_enpty   | 1     | 1      |                                                           |                                          |

| ∽ state           | 4     | 4      | 1                                                         | 0                                        |

| ∽ del taT_cnt     | 1260  | 1260   | 1278 X 1279 X 1280 X 1281 X 1282 X 1283 X 1284 X 1285 X 0 | <u>X 1 X 2 X 3 X 4 X 5 X 6 X 7 X</u>     |

| ∽ hi t_cnt        | 137   | 137    | 1                                                         | 0                                        |

| ∽ t0_1            | 1362  | 1362   | 13626 Х                                                   | 17001                                    |

| ∽ t0_2            | 1021  | 1021   | 10217 X                                                   | 13626                                    |

| ∽ t0_3            | 6841  | 6841   | 6841 X                                                    | 10217                                    |

|                   |       |        |                                                           |                                          |

|                   |       | 4 >    |                                                           |                                          |

| Waveform captured | Jun 1 | 8, 201 | 17 2:59:40 PM                                             | X: -50 • 0: -50 • Δ(X-0): 0              |

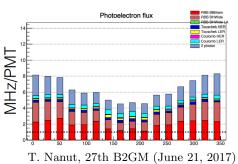

• Photon Flux significantly above desired levels

#### Beam Background

- 8 MHz/PMT

- 2 64 MHz/Board Stack

- 3 256 MHz/TOP Bar

< D > < B >

## t0s in presence of Background (electronic noise)

| Bus/Signal        | х     | 0    | 100 | -90 | -80   | -76   | -61  |    | 50<br> | -40   | - 30 |       | 20   | -10  |      | 10   |       | 20    | 30<br> | 40    | 50 | 60     | 70     | 8     | 0<br> | 90<br> | 100   | 110   | 120   | 130  | 140  | 150     |

|-------------------|-------|------|-----|-----|-------|-------|------|----|--------|-------|------|-------|------|------|------|------|-------|-------|--------|-------|----|--------|--------|-------|-------|--------|-------|-------|-------|------|------|---------|

| ∾ t0<1> *         | 0000! | 000! |     |     | 00005 | 763   |      |    |        |       | 0000 | 5916  |      |      |      |      |       |       |        |       |    | 000059 | 88     |       |       |        |       |       |       |      | 000  | )5A86   |

| ≻ t0<2>           | 00001 | 000X |     |     |       |       |      |    |        |       |      |       |      |      |      |      |       | C     | 00000  | 000   |    |        |        |       |       |        |       |       |       |      |      |         |

| ⊢ t0<3>           | 0000! | 000! |     |     |       | 00005 | 85 C |    |        |       |      | 0     | 0005 | BEC  |      | )    | (     | 00055 | 976    |       |    |        | 000054 | A0A   |       |        | χ     |       |       | 0000 | 5A99 |         |

| - t0<4>           | 0000! | 000! |     |     | 00005 | 7C2   |      |    |        |       | 00   | 0058  | 4C   |      |      |      |       | 00    | 00581  | 03    | X  |        | 00     | 00059 | 40    |        |       | 0     | 00059 | 5    |      | 00005A  |

| ≻ t0<5>           | 0000! | 000! |     |     | 000   | 5468  |      |    |        |       | 0000 | 054F1 |      |      | X    |      |       | 00    | 00557  | 0     |    |        |        |       |       | 000    | 05608 |       |       |      |      | 0000569 |

| ⊶ t0<6>           | 0000! | 000! |     |     |       |       |      |    |        |       |      |       |      |      |      |      |       | 0     | 0005   | 502   |    |        |        |       |       |        |       |       |       |      |      |         |

| ≻ t0<7>           | 00001 | 0001 |     | 000 | 05580 |       |      | 00 | 10055F | 7     |      |       |      | 0000 | 567A |      | X     |       | 000    | 056FE |    | X      | 000    | 00578 | 4     | _X_    |       | 00    | 05808 |      | X    | 0000    |

| ≻ t0<8>           | 00003 | 000  |     | 0   | 00033 | 64    | Х    |    | 00     | 00033 | E3   |       |      |      |      | 0000 | 03469 |       |        | Х     |    | 000    | 34E2   |       |       |        |       | 00003 | 57F   |      | χ    | 000035  |

| trg_fifo_empty_1  | 1     | 1    |     |     |       |       | l    |    |        |       |      |       |      |      |      |      |       |       |        |       |    |        |        |       |       |        |       |       | T     |      |      |         |

| trg_fifo_empty_2  | 1     | 1    |     |     |       |       |      |    |        |       |      |       |      |      |      |      |       |       |        |       |    |        |        |       |       |        |       |       |       |      |      |         |

| trg_fifo_empty_3  | 1     | 1    |     |     |       |       |      |    |        | J     |      |       |      |      |      | T    |       |       |        |       |    |        |        |       |       |        | J     |       |       |      |      |         |

| -trg_fifo_empty_4 | 1     | 1    |     |     |       |       |      |    |        |       |      |       |      |      |      |      |       |       |        |       | J  |        |        |       |       |        |       |       |       |      |      |         |

| -trg_fifo_empty_5 | 1     | 1    |     |     |       |       |      | Т  |        |       |      |       |      |      | T    |      |       |       |        |       |    | U      |        |       |       |        |       |       |       |      |      |         |

| -trg_fifo_empty_6 | 1     | 1    |     |     |       |       |      |    |        |       |      |       |      |      |      |      |       |       |        |       |    |        |        |       |       |        |       |       |       |      |      |         |

| -trg_fifo_empty_7 | 1     | 1    |     |     |       | ľ     |      |    |        |       |      |       |      |      |      |      | l     |       |        |       |    | l      |        |       |       |        |       |       |       |      | U    |         |

| trg_fifo_empty_8  | 1     | 1    |     |     |       |       | ľ    |    |        |       |      |       | l    |      |      |      |       |       |        | 1     |    |        |        |       |       |        |       |       |       |      | U    |         |

| (                 | < >   |      | (   |     |       |       |      |    |        |       |      |       |      |      |      |      |       |       |        |       |    |        |        |       |       |        |       |       |       |      |      |         |

- Triggers are too frequent in presence of background since every timestamp arrive at UT3 are processed

- This problem is already known from a software simulation

- Possible solution: Run Trigger algorithm only during the arrival of timestamps belong to a signal

Image: A matrix

- Initially, TSs go to "Shift register" and continuously monitored by "Data redirection" (path 1)

- O whenever  $\Delta T < \text{THRESHOLD}$

- i Stop taking TSs from FIFO

- ii Recover the 6 TS which is already in Shift reg.

(path 2& 4)

Continue to take TSs from FIFO, after recovering 6 TS in shift reg. (path 3& 4)

- FIFO shift register enable Data redirection. Trigger FSM

- Signal identification efficiency should be maximized by optimizing THRESHOLD and DEPTH

## Firmware with IHTD

- shiftreg\_cnt

- shiftreg\_full

- $\bullet$  deltat\_threshold\_flag

- shiftreg\_recovery\_flag

| 👹 Waveform - DEV:0 MyDev                                                                                               |                              | ce en a                      | NOOD INUT     | MALE ALL ALL ALL                        |                                         |                     |                     |                 |             |             | ් ක් 🗵                                  |

|------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|---------------|-----------------------------------------|-----------------------------------------|---------------------|---------------------|-----------------|-------------|-------------|-----------------------------------------|

| M waverorm - DEV:0 MyDev                                                                                               | iceo Q                       |                              |               |                                         |                                         |                     |                     |                 |             |             |                                         |

| Bus/Signal                                                                                                             | х                            | 0                            | .20 -115 -    | 9 -105 -1 0 -95 -90 -85                 |                                         | -65 -60 -55 -50     |                     |                 |             | -5 0        | 5 1                                     |

| ∽ shi ftreg_cnt                                                                                                        | 0                            | 0                            | 0             | 12346 / 6 _543211                       |                                         |                     |                     | 0               |             |             | ^                                       |

| -shiftreg_full                                                                                                         | 0                            | 0                            |               | i <u>_</u>                              |                                         |                     |                     |                 |             |             | _                                       |

| <pre>- deltat_threshold_flag</pre>                                                                                     | 0                            | 0                            |               |                                         |                                         |                     |                     |                 |             |             | _                                       |

| -shiftreg_recovery_flag                                                                                                | 0                            | 0                            |               |                                         |                                         |                     |                     |                 |             |             | _                                       |

| ⊶ state                                                                                                                | 0                            | 0                            |               | • 0000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 000000000000000000  | 4XXXXXXX            | 4 XX            |             | 0           |                                         |

| ~ t0                                                                                                                   | 7426                         | 7426                         |               |                                         |                                         | 7426                |                     |                 |             | X           | 108                                     |

| -t0_valid                                                                                                              | 0                            | 0                            |               |                                         |                                         |                     |                     |                 |             |             |                                         |

|                                                                                                                        | 4 1                          | 4 1                          | 4             |                                         |                                         | -                   |                     |                 |             |             |                                         |

| Waveform captured Aug 18, 2                                                                                            |                              |                              |               |                                         |                                         |                     | Х:                  | -500 4 🕨 0:     | -500 4 F Å  | (X-0):      | 0                                       |

| a                                                                                                                      | _                            | _                            |               |                                         |                                         |                     |                     |                 |             |             |                                         |

| 🍘 Waveform - DEV:0 MyDev                                                                                               | ice0 Q                       |                              |               |                                         |                                         |                     |                     |                 |             |             | ් ් 🛛                                   |

| Bus/Signal                                                                                                             |                              |                              | 225 - 220 - 2 | 15 -210 -205 -200 -195 -190             | -185 -180 -175                          | -170 -165 -160 -155 | -150 -145 -         | 0 -135 -130 -12 | 5 -120 -115 | -110 -105 - | 100 -                                   |

| bus/signal                                                                                                             | x                            | U                            | Junihard      | and an developed and see by             | والتبيينا بترتيا بت                     |                     | Ver la real de la V |                 |             |             | dunu.                                   |

| eus/signal                                                                                                             | X<br>6                       | 0                            | ليتباليتنا    | <u>ll</u> 6                             | uluuluulu                               | - deserved and a    | 54321               | and and and     | <u></u>     | uluuluu     | <u></u> *                               |

|                                                                                                                        |                              | 0                            |               | يتا يتصابين التسبا يتصابين              | ulundund                                | -deceloration       |                     | uuluuluul       |             | uluuluu     | <u></u> ^                               |

| ⊶ shiftreg_cnt                                                                                                         |                              | 6                            | <u></u>       | يتا يتصابين التسبا يتصابين              |                                         | ndundandanda        |                     |                 |             | uluuluu     | ^                                       |

| • shiftreg_cnt<br>- shiftreg_full                                                                                      | 6                            | 6<br>1<br>0                  |               | يتا يتصابين التسبا يتصابين              | <u>uluuluul</u>                         |                     | 503210              |                 | 0           |             |                                         |

| <pre>shiftreg_cnt _shiftreg_full _deltat_threshold_flag</pre>                                                          | 6<br>1<br>0                  | 6<br>1<br>0                  |               | يتا يتصابين التسبا يتصابين              |                                         |                     | 503210              |                 | 0           |             |                                         |

| <ul> <li>shiftreg_cnt</li> <li>shiftreg_full</li> <li>deltat_threshold_flag</li> <li>shiftreg_recovery_flag</li> </ul> | 6<br>1<br>0                  | 6<br>1<br>0                  |               | 6                                       |                                         | 467                 | 503210              |                 | 0           |             |                                         |

| shiftreg_cnt     shiftreg_full     deltat_threshold_flag     shiftreg_recovery_flag     state                          | 6<br>1<br>0<br>0             | 6<br>1<br>0<br>0<br>467      |               | 6                                       |                                         |                     | 503210              |                 | 0           |             |                                         |

| • shiftreg_nt<br>- shiftreg_full<br>delta_threshold_flag<br>- shiftreg_recovery_flag<br>• state<br>• t0<br>- t0_valld  | 6<br>1<br>0<br>0<br>467      | 6<br>1<br>0<br>0<br>467<br>0 |               | 6                                       | r                                       |                     | 503210              |                 | 0           |             |                                         |

| shiftreg_nt     shiftreg_full     deltat_threshold_flag     shiftreg_recovery_flag     state     t0     t0_valld       | 6<br>1<br>0<br>0<br>467<br>0 | 6<br>1<br>0<br>0<br>467<br>0 |               | 6                                       | ndunalaanda<br>p                        |                     | 503210              |                 | l<br>0      |             | >>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>> |

$$\tilde{t0} = \frac{\left(\sum_{i=1}^{i=16} t0_i L_i\right)}{\left(\sum_{i=1}^{i=16} L_i\right)}$$

- t0<sub>1</sub>-t0<sub>8</sub> on UT3(1) and t0<sub>9</sub>-t0<sub>16</sub> on UT3(2)

- All t0s on UT3(1) are send to UT3(2) (4-lane AURORA with each lane is 5.08 Gbps)

- All t0s are temporarily stored on a RAM until t0 is estimated

< D > < B >

# Combined t0 on UT3(2)

| sun_logL 0    |            | 500 -460 -420 -380 -340 -300 -260 -220 -180 -140 -100 -60 | -20 20        | 60 100 140 18 |                                       | 460 50          |

|---------------|------------|-----------------------------------------------------------|---------------|---------------|---------------------------------------|-----------------|

|               | 0000 0000  | 000000063054232                                           |               | X             | 00000005DE34F01                       |                 |

| sun_t0°logi   | 0000 0000: | 000018E0276C0669                                          |               | X             | 0000123F706DD782                      |                 |

| nean_t0       | 0000 0000  | 000000000004811000000019749117                            |               | X             | 0000000000031C1000000025F016F1        |                 |

| counter       | 64 39      | 0                                                         | )             | X.            | 0                                     |                 |

| state_combine | 1 1        | 0                                                         | X 1           | X             | 0                                     |                 |

| RAM<1>        | 0000 0000  | 00000000                                                  |               | X             | 00000000                              |                 |

| RAM<2>        | 0000 0000  | 00000000                                                  |               | X             | 00000000                              |                 |

| RAM<3>        | 0000 0000  | 00000000                                                  |               | XX            | 00000000                              |                 |

| RAM<4>        | 0000 0000  | 00000000                                                  |               | XX            | 00000000                              |                 |

| RAM <s></s>   | 0000 0000  | 00000000                                                  | X             | Х             | 00000000                              |                 |

| RAM<6>        | 0000 0000: | 00000000                                                  | (000031       | că            | 00000000                              |                 |

| RAM<7>        | 0000 0000  | 00000000                                                  |               | X             | 00000000                              |                 |

| RAM<8>        | 0000 0000  | 00000000                                                  |               | X             | 00000000                              |                 |

| RAM<9>        | 0000 0000  | 00000000                                                  | 2000          | Х             | 00000000                              |                 |

| RAM<10>       | 0000 0000  | 00000000                                                  | <b>6</b> 0    | X             | 00000000                              |                 |

| RAN<11>       | 0000 0000: | 00000000                                                  | \$0000.       | Х             | 00000000                              |                 |

| RAM<12>       | 0000 0000  | 00000000                                                  | X00           | X             | 00000000                              |                 |

| RAN<13>       | 0000 0000: | 00000000                                                  | X 000031C3    | χ             | 00000000                              |                 |

| RAM<14>       | 0000 0000  | 00000000                                                  | Х.            | X             | 00000000                              |                 |

| RAN<15>       | 0000 0000: | 00000000                                                  | 000031        | άX            | 00000000                              |                 |

| RAM<16>       | 0000 0000: | 00000000                                                  | ) <b>0</b> 00 | X             | 00000000                              |                 |

| reset_RAM     | 0 0        |                                                           |               | 1             |                                       |                 |

| t0_Aurora :   | 1CBC BCBCI |                                                           |               |               | · · · · · · · · · · · · · · · · · · · | (1) (1) (m) (m) |

| Bar_number    | EE         | E                                                         | X E XXX       | E X           | E                                     |                 |

| rx_src_rdy_n  | 1 1        |                                                           |               |               |                                       |                 |

| t0_Contoller  | 1C1C 1CBC: |                                                           |               |               |                                       |                 |

|               | E E        | Ε                                                         | X E 30        | E X           | E                                     |                 |

| Bar_nunber    |            |                                                           | 1 10          |               |                                       |                 |

Э.

# Combined t0 on UT3(2)

| Bus/Signal    | х    | 0    | -235 -215 -195 -175 -155 -135 -115 -95 -75 -55 -35 -15 | <b>5</b> |           | 25 45    |      | 65 85 105 125 145 165 185 205 225 245 |

|---------------|------|------|--------------------------------------------------------|----------|-----------|----------|------|---------------------------------------|

| - sun_logL    | 0000 | 0000 | 000000063054232                                        |          |           |          | Х    | X 00000005DE34F01                     |

| - sun_t0°logi | 0000 | 0000 | 000018E0276C0669                                       |          |           |          | X    | X 0000123F706DD782                    |

| - nean_t0     | 0000 | 0000 | 00000000004811000000019749117                          |          |           |          |      | X 000000000031C1000000025F016F1       |

| - counter     | 6    | 39   | 0                                                      |          |           |          | 222  | 0                                     |

| state_combine | :    | 1    | (                                                      |          | _1        |          | 1    | 0                                     |

| - RAM<1>      | 0000 | 0000 | 0000000                                                | 1        | <u> </u>  | X        |      | 00000000                              |

| - RAM<2>      | 0000 | 0000 | 0000000                                                |          |           |          |      | 00000000                              |

| - RAM<3>      | 0000 | 0000 | 00000000                                               |          |           |          |      | 00000000                              |

| - RAM<4>      | 0000 | 0000 | 00000000                                               |          |           |          |      | 00000000                              |

| - RAM <s></s> | 0000 | 0000 | 00000000                                               |          |           | )60      | o)   |                                       |

| - RAM<6>      | 0000 | 0000 | 0000000                                                |          |           | 00003100 |      | 00000000                              |

| - RAM<7>      | 0000 | 0000 | 00000000                                               |          |           |          | DC   | 00000000                              |

| - RAM<8>      | 0000 | 0000 | 00000000                                               |          |           |          |      | 00000000                              |

| RAM<9>        | 0000 | 0000 | 00000000                                               |          |           | 000031   | C1 ) | 00000000                              |

| RAM<10>       | 0000 | 0000 | 00000000                                               |          |           | X 00003  | C1.  | 00000000                              |

| RAM<11>       | 0000 | 0000 | 00000000                                               |          | X         | 0000310  |      | 00000000                              |

| - RAM<12>     | 0000 | 0000 | 0000000                                                |          |           | X 00003  | 100  | 00000000                              |

| RAM<13>       | 0000 | 0000 | 00000000 X                                             |          |           | 31C3     |      | 00000000                              |

| RAM<14>       | 0000 | 0000 | 00000000                                               |          |           | X 0000   | 10   | 00000000                              |

| RAM<15>       | 0000 | 0000 | 00000000                                               | X        | 0         | 00031C1  |      | 00000000                              |

| RAM<16>       | 0000 | 0000 | 00000000                                               | H        | $\supset$ | 000031   | 0    | 00000000                              |

| reset_RAM     | 0    | 0    |                                                        |          | _         |          |      |                                       |

| t0_Aurona     | 1080 | BCBC |                                                        | 2.07     | ÷0.       |          | 200  |                                       |

| Bar_number    |      | E    | E                                                      |          | Е         | 1.123    |      | E XX E                                |

| rx_src_rdy_n  | :    | 1    |                                                        |          |           | 1 mm     |      |                                       |

| t0_Contoller  | 1010 | 1CBC |                                                        | 107      | 11        |          | 33   |                                       |

|               |      | E    | E                                                      |          | Ε         |          |      | ε ΧΧ ε                                |

| Bar_number    |      |      |                                                        |          |           | 0 00 0   |      |                                       |

モー

(日) (四) (里) (里)

# Combined t0 on UT3(2) (latency added)

| Bus/Signal              | x            | 0         | 500 -460 -420 -380 -340 -300 -260 -220 -180 -140 -100 | -60 -20 20 60 100 | 140 180 220 260 300 340 380 420 460 5  |

|-------------------------|--------------|-----------|-------------------------------------------------------|-------------------|----------------------------------------|

| ⊳ <mark>sun_1ogL</mark> | 00000006558  |           | 0000000655E7EF6                                       |                   | 000000056F63A1D                        |

| sun_t0*logL             | 000000684880 | 0000030FD | 0000006848807813                                      | X                 | 0000030FD8DFCFDE                       |

| rean_t0                 | 000000000000 | 000000000 | 00000000001F55000000031F08665                         | X                 | 00000000000000000000000000000000000000 |

| nean_t0_valid           | 0            | 1         |                                                       |                   |                                        |

| ⊳ counter               | 46           | 0         | 0                                                     | Xunnann)          | 0                                      |

| ⊳ state_combine         | 2            | 0         | 0                                                     | χ 1 🕱             | 0                                      |

| ► RAM<1>                | 00000905     | 00000000  | 00000000                                              | X X               | 00000000                               |

| ~ RAM<2>                | 00000904     | 00000000  | 00000000                                              | XX                | 00000000                               |

| ► RAM<3>                | 00000905     | 00000000  | 00000000                                              | X0000090K         | 00000000                               |

| ► RAM<4>                | 00000905     | 00000000  | 00000000                                              | XX                | 00000000                               |

| RAM-S>                  | 00000903     | 00000000  | 00000000                                              | X X               | 00000000                               |

| - RAM<6>                | 00000903     | 00000000  | 00000000                                              | X0000 X           | 00000000                               |

| - RAM<7>                | 00000905     | 00000000  | 00000000                                              | X X               | 00000000                               |

| - RAM<8>                | 00000902     | 00000000  | 00000000                                              | XX                | 00000000                               |

| - RAM<9>                | 00000902     | 00000000  | 00000000                                              | XX                | 00000000                               |

| - RAM<10>               | 00000902     | 00000000  | 00000000                                              | XX                | 00000000                               |

| - RAM<11>               | 00000905     | 00000000  | 00000000                                              | X X               | 00000000                               |

| - RAM<12>               | 00000902     | 00000000  | 00000000                                              | X                 | 00000000                               |

| ≻ RAM<13>               | 00000905     | 00000000  | 00000000                                              | X0000090X         | 00000000                               |

| RAM<14>                 | 00000902     | 00000000  | 00000000                                              | XX                | 00000000                               |

| ► RAM<15>               | 00000903     | 00000000  | 00000000                                              | XX                | 00000000                               |

| - RAM<16>               | 00000905     | 00000000  | 00000000                                              | XX                | 00000000                               |

| reset_RAM               | 0            | 0         |                                                       |                   |                                        |

| ≻ t0_Aurora             | 1CBC1CBC     | 10101010  |                                                       | *****             |                                        |

| Bar_number              | E            | E         | E                                                     | XX E XXX          | E                                      |

| - rx_src_rdy_n          | 1            | 1         |                                                       | 1 111             |                                        |

| - t0_Contoller          | BC1CBC1C     | BC1CBC1C  |                                                       |                   |                                        |

| - Bar_number            | E            | E         | E                                                     | X E XXX           | E                                      |

| -valid                  | 0            | 0         |                                                       |                   |                                        |

|                         |              |           |                                                       |                   |                                        |

| <                       | 4 II   F     |           | ٠                                                     |                   |                                        |

æ

A D >

A D >

A

| Bus/Signal     | х            | 0         |       | -10  | -5     |            | 5        | 10            | 15      | 20      | 25      | 30    | 35      | 40     | 45   | 50         | 55     | 61  |        | 70    | 0. <sup>75</sup>                             | 80     | 85     | 90      | 95   | 100   | 105   | 110 |  |

|----------------|--------------|-----------|-------|------|--------|------------|----------|---------------|---------|---------|---------|-------|---------|--------|------|------------|--------|-----|--------|-------|----------------------------------------------|--------|--------|---------|------|-------|-------|-----|--|

| sun_logL       | 0000000055FE | 000000005 |       |      |        | - <b>T</b> |          |               | 00000   | 000655  | E7EF6   |       |         |        |      |            | X      |     |        |       |                                              |        | 000000 | 056F63A | 1D   |       |       |     |  |

| - sun_t0*logL  | 0000030F080F | 0000030FD |       |      |        |            |          |               | 00000   | C684880 | 07813   |       |         |        |      |            | X      |     |        |       |                                              | 0      | 000030 | DBDFCF  | DE   |       |       | -   |  |

| nean_t0        |              | 000000000 |       |      |        |            |          |               | 00      |         | 00001F5 |       | 000031F | 08665  |      |            |        |     |        |       | 0000000000000000000000000002BF21C87          |        |        |         |      |       |       |     |  |

| mean_t0_valid  | 0            | 1         |       |      |        |            |          |               |         |         |         |       |         |        |      |            |        |     |        |       | <u>п                                    </u> |        |        |         |      |       |       |     |  |

| - counter      | 0            | 0         |       |      | 0      |            |          |               | 33660   | 89000X  | 00000   | 00000 | 00000   | 200000 | 0000 | 00000      | 2000   |     |        |       |                                              |        | 0      |         |      |       |       | _   |  |

| state_combine  | 3            | 0         |       |      | 0      |            |          |               |         |         |         |       | 1       |        |      |            | )28    | (   |        |       |                                              |        |        | 0       |      |       |       | -   |  |

| - RAM<1>       | 00000905     | 00000000  |       |      |        |            |          | 000           | 000000  |         |         |       |         |        |      | 00000      | 105    | X   |        |       |                                              |        | 000    |         |      |       |       | _   |  |

| - RAM<2>       | 00000904     | 00000000  |       |      |        |            |          | 0             | 0000000 |         |         |       |         |        |      | 0000       | 0904   | X   |        |       |                                              |        | 000    | 00000   |      |       |       | -   |  |

| RAM<3>         | 00000905     | 00000000  |       |      | 000000 | 0          |          | $\sim$        |         |         |         | 0     | 0000905 |        |      |            |        | Х   |        |       |                                              |        | 000    | 00000   |      |       |       | _   |  |

| - RAM<4>       | 00000905     | 00000000  |       |      |        |            |          |               | 0000000 | 0       |         |       |         |        |      | 000        | 20600  | Х   |        |       |                                              |        | 000    | 00000   |      |       | -     | _   |  |

| RAM(S>         | 00000903     | 00000000  |       |      |        |            |          | 000000        | 000     |         |         |       |         | χ      | 00   | 000903     |        | Х   |        |       |                                              |        | 000    | 00000   |      |       |       | _   |  |

| - RAM<6>       | 00000903     | 00000000  |       |      | 0000   | 000        |          |               | X       |         |         |       | 00000   | 03     |      |            |        | Х   |        |       |                                              |        | 000    | 00000   |      |       | -     | _   |  |

| - RAM<7>       | 00000905     | 00000000  |       |      |        |            |          |               | 0000    |         |         |       |         | (      |      | 0000090    | 5      | Х   |        |       |                                              |        | 000    | 00000   |      |       |       | _   |  |

| - RAM<8>       | 00000902     | 00000000  |       |      |        |            | 0000000  |               |         |         |         |       |         |        |      | )(         | 000090 | X.  |        |       |                                              |        | 000    | 00000   |      |       | -     | _   |  |

| - RAM<9>       | 00000902     | 00000000  |       |      |        |            | 00000000 |               |         |         |         |       |         |        | _)(• | 0000902    | 2X     |     |        |       |                                              | 000    | 00000  |         |      |       | _     |     |  |

| - RAM<10>      | 00000902     | 00000000  |       |      |        |            | 00000000 |               |         |         |         |       |         |        |      | 000009     | o¥     |     |        |       |                                              | 000    | 00000  |         |      | -     | _     |     |  |

| - RAM<11>      | 00000905     | 00000000  |       |      |        |            |          |               | 0000    |         |         |       |         | (      |      | 0000090    | 5      | Х   |        |       |                                              |        | 000    | 00000   |      |       |       | _   |  |

| - RAM<12>      | 00000902     | 00000000  |       |      |        |            |          |               | 00      | 000000  |         |       |         |        |      |            | X.     | Х   |        |       |                                              |        | 000    | 00000   |      |       |       |     |  |

| - RAM<13>      | 00000905     | 00000000  |       |      | 000000 | 0          |          |               |         |         |         | 0     | 0000905 |        |      |            |        | Х   |        |       |                                              |        | 000    | 00000   |      |       | _     | _   |  |

| - RAM<14>      | 00000902     | 00000000  |       |      |        |            |          | 0             | 0000000 |         |         |       |         |        |      | 0000       | 902    | Х   |        |       |                                              |        | 000    | 00000   |      |       |       |     |  |

| - RAM<15>      | 00000903     | 00000000  |       |      |        |            | 00       | 000000        | 0       |         |         |       | X       |        | 000  | 00903      |        | X   |        |       |                                              |        | 000    | 00000   |      |       |       | _   |  |

| - RAM<16>      | 00000905     | 00000000  |       |      |        |            |          |               | 000000  | 00      |         |       |         |        |      | X 00       | 206000 | χ   |        |       |                                              |        | 000    | 00000   |      |       | -     | _   |  |

| reset_RAM      | 1            | 0         |       |      |        |            |          |               |         |         |         |       |         |        |      |            |        | 1   |        |       |                                              |        |        |         |      |       |       |     |  |

| - t0_Aurona    | BCBCBCBC     | 10101010  | 20-20 | 0000 |        | _xxx       | 00000    | XX            | 00000   |         | 00000   | 00000 | 000000  | 000000 |      | $\odot$    | 0000   | )(  | 2000   | XXX   |                                              | 000000 |        | 00000   | 0000 | 00000 | XXXXX | _0  |  |

| Bar_nunber     | E            | E         |       | Е    |        | DØE        | 6        |               | E       |         |         |       | E000    | XE)    | (    |            |        |     |        |       |                                              | E      |        |         |      |       | -     | _   |  |

| rx_src_rdy_n   | 1            | 1         |       |      |        | ╖╴         |          |               |         |         |         | 1     |         | υī     |      |            |        |     |        |       |                                              |        |        |         |      |       | -     |     |  |

| - t0_Contoller | 1CBC1CBC     | BC1CBC1C  | 000   | 0000 | 010    | XXXXXX     | 0000     | $X \supset X$ | 000000  | 200000  |         | 00000 | 00000   | 000000 | 000  | $\bigcirc$ | 00000  | -00 | 200000 | XXXXC | ¢⊡00                                         | 000000 |        | 00000   | 00   | 00000 | 00000 |     |  |

| Bar_number     | E            | E         |       | Е    |        | _)%        | 08(      |               |         | E       |         |       |         | E)(    | (    |            | _      |     |        |       |                                              | E      |        |         |      |       | -     | _   |  |

| -valid         | 0            | 0         |       |      |        | _л         | Л        |               |         |         |         | П     | Л       |        |      |            |        | _   |        |       |                                              |        |        |         |      |       |       | _   |  |

|                |              |           |       |      |        |            |          |               |         |         |         |       |         |        |      |            |        |     |        |       |                                              |        |        |         |      |       |       |     |  |

| (              |              | • • • • • | 4     | _    | _      |            |          |               |         |         |         |       |         |        |      | _          | 11     | _   |        |       |                                              | _      |        |         |      | _     |       | _   |  |

#### Latency

- Latency estimated for single Bar by injecting calibration pulses in to FEE

- Latency depends on number of hits and have contribution from AURORA, XILINX cores used for weighted sum of t0 etc.

- Overall expected latency below 2.5 us

- $\bullet\,$  Timestamping is implemented in all latest FEE FW and reliably transmitting them to UT3 at 5.08 Gbps

- The algorithms for collecting and combining t0 decisions from individual bars have been designed and tested at KEK

- TOP Trigger latency is measured and the value is well within maximum allowed limit

- TOP Trigger FW with Instantaneous Hit Time Density (IHTD) is designed and tested at Pittsburgh. Working on optimization of various parameters to get best possible performance of Trigger FW.

- Soon start working on interface to GDL.